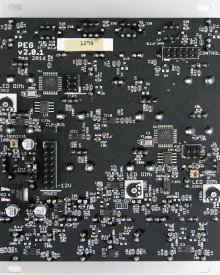

4ms Pingable Envelope Generator

The Pingable Envelope Generator (PEG) from 4ms is a dual envelope generator whose envelope lengths are set by incoming clocks or "pings".

The PEG has full CV control of envelope shape, skew, and ping (clock) division/multiplication, as well as a plethora of triggering and cycling options (AD, AR, quantization, cycle), and a tap tempo button for each channel.

Features:

Basics:

Dual "pingable" envelope generator's total envelope time is set by a "ping"

Tap tempo button or incoming clock sets the ping time

Envelope time is a multiple or division of the ping time (from /8 to x8) set by Ping Div/Mult knob and CV

Curve knob and CV control the shape of the output envelope. Various combinations of exponential, linear, logarithmic, and interpolated curves are available for the rise and fall portions. Total envelope time is maintained throughout any curve selection.

Skew knob and CV control the ratio between rise and fall times without changing total envelope time

Scaling/shifting:

Scale knob is an attenuating inverter for main envelope output (Maximum 0V to +10V non-inverted, and Minimum -10V to 0V inverted).

Bi-polar button centers main envelope output around 0V (-5V to +5V output)

"+5V ENV" jack is a non-scaling output that always produces a 0V to +5V envelope, regardless of Scale and Bi-polar settings

"OR" jack outputs an analog OR of the two scaled envelope curves. This outputs the highest value from either envelope at any given moment, taking into account the Scale and Bi-polar controls.

Gate outputs:

End-of-Rise (EOR) gate output goes high when envelope finishes a rise portion, and goes low when envelope begins a rise portion

End-of-Fall (EOF) gate output goes high when envelope finishes a fall portion, and goes low when envelope begins a fall portion

Jumper for each channel changes EOR output to a Half-Rise gate output. The Half-Rise jack goes high when 50% of the time of the rise portion has elapsed, and goes low after 50% of the time of the fall portion. Using the Skew parameter, this jack provides a variable phase gate output useful for quadrature effects and clock phase shifting and trigger delay effects. Factory setting is EOR for red channel, Half-Rise for blue channel.

Triggering/cycling:

Cycle button for each channel forces envelope to self-cycle in sync with the ping clock (LFO mode). Button lights up when in cycle mode.

"T" jack toggles the state of both channels' Cycle button when a gate is applied

"QNT" jack for each channel triggers an envelope to start at the next quantized beat, with respect to the divided/multiplied ping clock. Holding a gate high on this jack causes the envelope to repeat.

"Async" jack for each channel causes an envelope to output immediately (asynchronously). Holding a gate high results in an AR envelope (rise-sustain-fall). If cycle mode is enabled, the envelope will continue to cycle at this new phase with respect to the ping clock. Phase can be reset to being in sync with the ping clock by pressing the cycle button or applying a pulse to the QNT jack.

CV input jacks:

CV control of Ping Div/Mult, Skew, and Curve using the CV jacks. Respective knobs set the center offset for the applied CV

CV of 0-10V will modulate the parameter's full range However, a 0-5V CV will modulate the parameter within a very useful range.

Module size:

The PEG is 20HP and 1.6 inches (40mm) deep.

Power consumption:

A jumper selects using +5V from the power supply, or generating +5V on-board from the +12V rail.

+12V rail:

59mA max with jumper selecting external 5V

105mA max with jumper selecting internal 5V.

+5V rail:

38mA max with jumper selecting external 5V

not used (0mA) with jumper selecting internal 5V.

-12V rail:

34mA max

* こちらの商品は在庫切れの場合、発送まで約1ヶ月かかる場合がございます。ご了承ください...